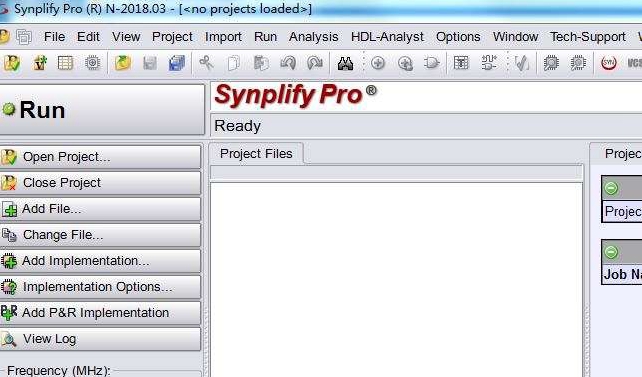

If you wish to create a hierarchical project, make sure the top-level design file is at the bottom of the Source Files list by selecting the file and dragging it to the bottom of the list. Select your design file(s) and choose the Open button to add the file(s) to your Source Files list in the Synplify window.The Add Source Files dialog box is displayed. Choose the Add button from the Project window.Choose New (File menu) to display the New dialog box, then select Project from the list.

On a PC, double-click the synplify.exe icon in your ¥synplicity¥bin directory. On a UNIX workstation, type synplify at a UNIX prompt from your working directory.

#Synplify pro output single edf file software#

Go to Creating VHDL Designs for Use with MAX+PLUS II Software or Creating Verilog HDL Designs for Use with MAX+PLUS II Software for more information on HDL design entry. v, using the MAX+PLUS II Text Editor or another standard text editor and save it in a working directory.

#Synplify pro output single edf file how to#

The information presented here describes only how to use VHDL or Verilog HDL files that have been processed by Synplify software. The MAX+PLUS II Compiler can process a VHDL or Verilog HDL file that has been synthesized by Synplify software, saved as an AHDL TDF or an EDIF netlist file, and imported into the MAX+PLUS II software.

edf) that can be processed by the MAX+PLUS ® II Compiler. Journal of Embedded Computing IOS Press You can create and process VHDL or Verilog HDL files and convert them to Altera ® Hardware Description Language (AHDL) Text Design Files (. Comparing results with non-adaptive implementations verify the fact that our approach improves system's robustness to scene variations and outperforms the traditional implementations. Experimental results on a set of scenes advocate the fact that our system works effectively for different scenario of events through reconfiguration.

We justify the need for dynamic adaptation of the system through scenarios and applications. We exploit reconfigurable hardware devices embedded in a number of networked cameras in order to achieve our goal. This feature is discussed in depth in a collaborative and dynamically adaptive object tracking system that has been built in our lab as the experimental framework of this study. Specifically we focus on dynamic adaptation of the system as a particular feature of such systems. This paper discusses the requirements of the aforementioned systems, their advantages and the issues involved in developing them. Examples include systems that use many randomly distributed sensing boards, each one having a fixed structure of computation resources and sensing devices, to autonomously detect events and take proper actions. Sensor, actuators and embedded computation resources used for implementing such systems usually exhibit regular local configurations, while the global structure of the subsystems is either not fixed a priori and can change at runtime or is not known. Many applications utilize deeply embedded sensors and actuators that are tightly coupled with the physical environment in order to perform their functionality. Reconfiguration in network of embedded systems: Challenges and adaptive tracking case study Reconfiguration in network of embedded systems: Challenges and adaptive tracking case study

0 kommentar(er)

0 kommentar(er)